### **DesignCon 2006** Track 5-WP2 : Chip and Package Co-Design

### Impedance Matching Techniques for VLSI Packaging

Author / Presenter:

Brock J. LaMeres, Ph.D.

**Co-Authors:**

Rajesh Garg Kanupriya Gulati Sunil P. Khatri, Ph.D Texas A&M University Texas A&M University Texas A&M University

### **Problem Statement**

- Reflections from interconnect will limit VLSI system performance

- This is caused by :

Parasitics of the Package Interconnect

Faster Risetimes in Off-chip Driver Circuitry

# Agenda

1) Package Interconnect Parasitics

2) Proposed Solution

**3) Experimental Results**

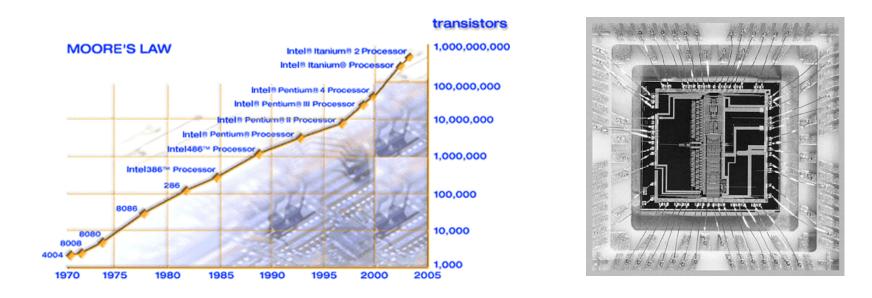

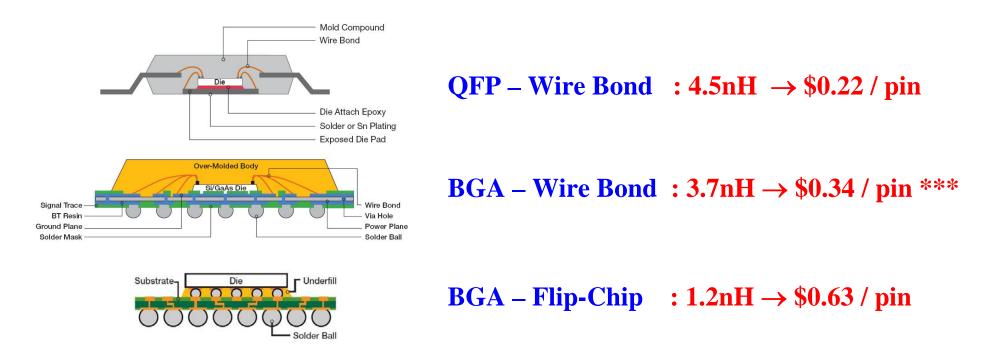

#### **Transistor Technology is Outpacing Package Technology**

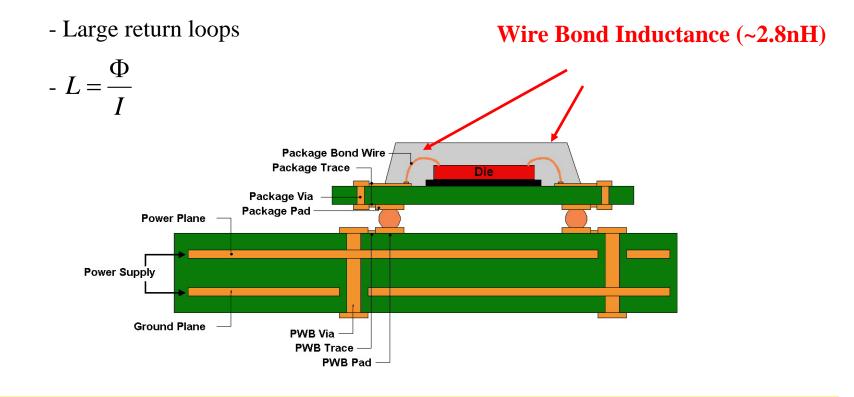

• Today's Package Interconnect Looks Inductive

- Long interconnect paths

• Inductive Interconnect Leads to Reflections

- Interconnect is not matched to system

- Reflections occur due to interconnect

#### • Aggressive Package Design Helps, but is expensive...

- Majority of VLSI design-starts are wire bonded

- Goal: Extend the life of wire bonded packages

# Why Now?

#### **Cost**

- Historically, the transistor delay has dominated performance.

- Inexpensive packaging has met the electrical performance needs.

### <u>Faster Risetimes</u>

- As transistors shrink, faster risetimes can be created.

- Everything in the package becomes a transmission line.

### **Impedance Matching**

- The impedance of the package is not matched to the system.

- This leads to reflections from the inductive wire bond in the package

### **Current Solution to Reflections**

### • Live with the Signal Path Reflections

1) Run the signals slow enough so that reflections are small

$$\Gamma = \frac{Z_L - Z_0}{Z_L + Z_0} < 10\%$$

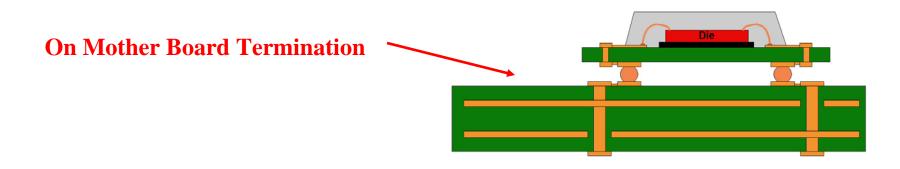

2) Terminate Signals on the Mother board so that reflections are absorbed

## **Current Solution to Reflections**

#### • Limitations of Approach

1) Run the signals slow enough so that reflections are small

• Limits System Performance

2) Terminate Signals on the Mother board so that reflections are absorbed

• This only eliminates primary reflections, the second still exists

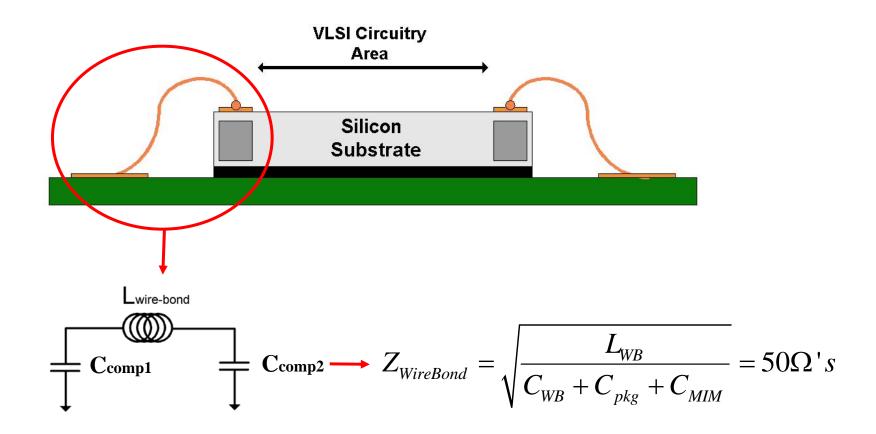

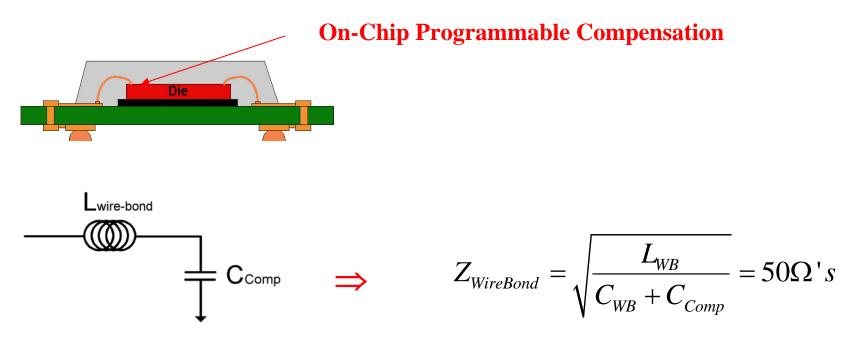

# **Proposed Solutions – Impedance Compensation**

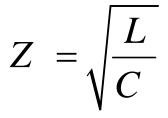

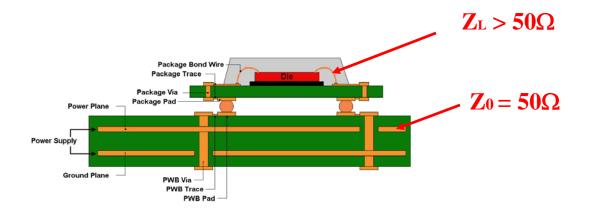

• Add Capacitance Near Bond Wire to Reduce Impedance

- Adding additional capacitance lowers the wire bond impedance

- Impedance can be matched to system, reducing reflections

$$Z_{WireBond} = \sqrt{\frac{L_{WireBond}}{C_{WireBond}}} \longrightarrow \text{Add Capacitance to lower Z}$$

### **Proposed Solutions – Impedance Compensation**

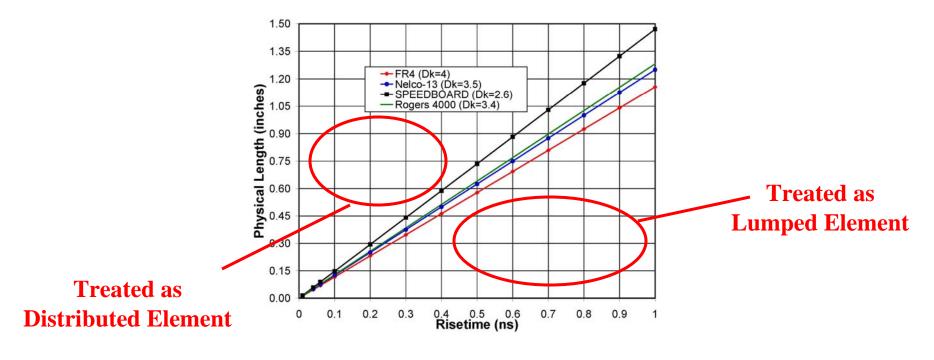

• If the capacitance is close to the wire bond, it will alter its impedance

- Electrical lengths less than 20% of risetime are treated as lumped elements

- For modern dielectrics, anything within 0.15" of wire bond is lumped

# **Proposed Solutions – Impedance Compensation**

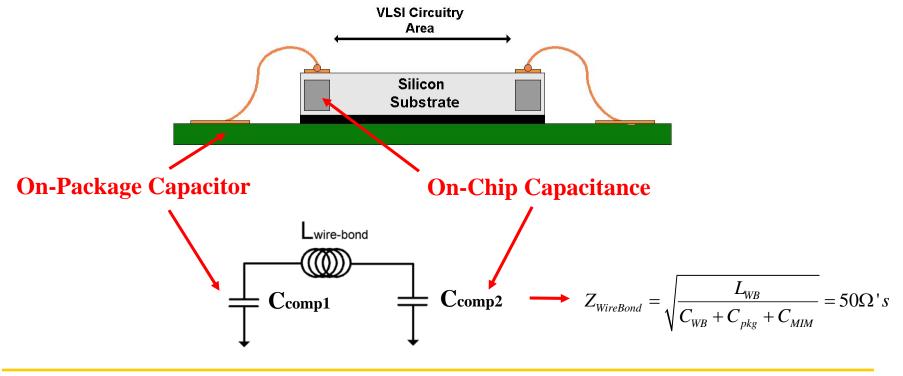

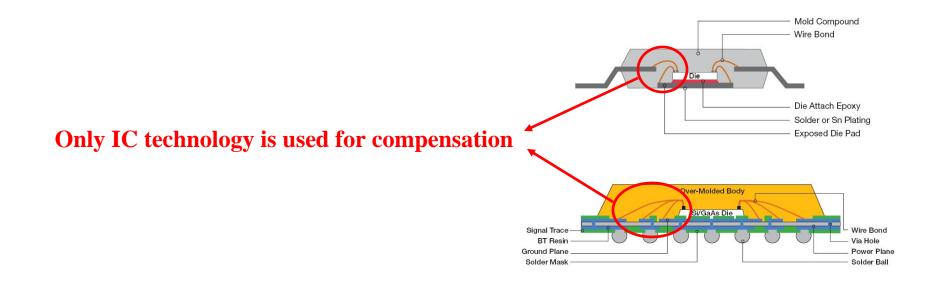

• Capacitance on the IC or Package is close enough to alter impedance

#### • Capacitor values chosen prior to fabrication

- Equal amounts of capacitance are used on-chip and on-package

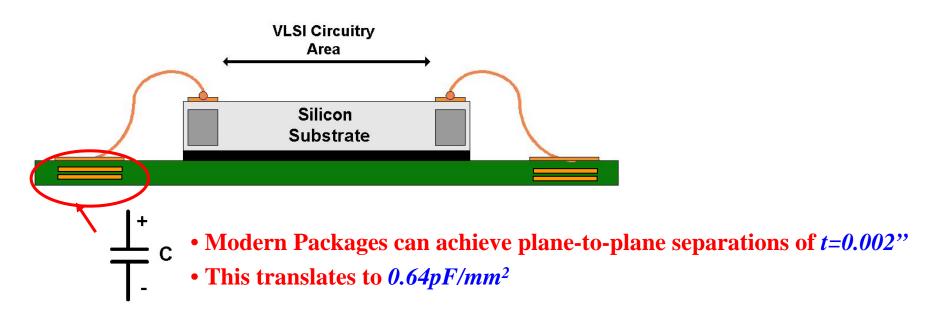

### On-Package Capacitors

- Embedded capacitor construction is used

- No components are needed, reducing package cost

- Capacitance values needed can be implemented using this construction

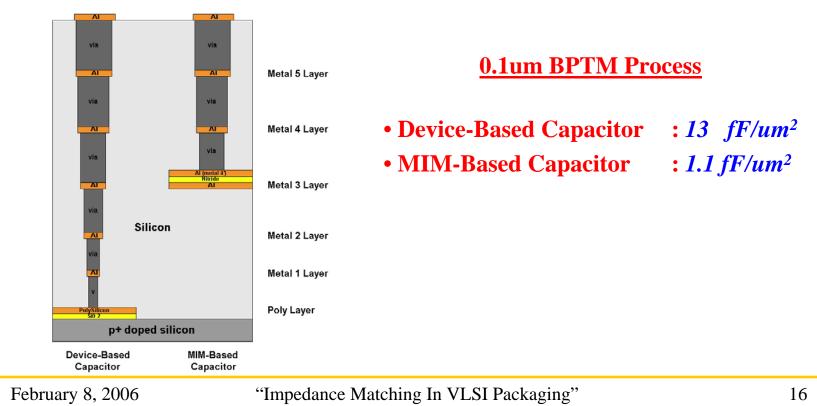

#### • **On-Chip Capacitors**

- Device and MIM capacitors are evaluated

- Targeting area beneath wire bond pad, which is typically unused

#### • Wire Bond Modeling

- Typical VLSI wire bond lengths range from 1mm to 5mm

- Electrical parameter extraction is used to find L and C or wire bond

| <b>Length</b> | L       | <u>C</u>    | <u>Z0</u> |

|---------------|---------|-------------|-----------|

| 1mm           | 0.569nH | 26fF        | 148Ω      |

| 2mm           | 1.138nH | 52fF        | 148Ω      |

| 3mm           | 1.707nH | <b>78fF</b> | 148Ω      |

| 4mm           | 2.276nH | 104fF       | 148Ω      |

| 5mm           | 2.845nH | 130fF       | 148Ω      |

### • On-Package Capacitor Sizing

- Capacitor values are found to match wire bond to  $50 \Omega$

- Area is evaluated for feasibility

| <u>Length</u> | Ccomp1   |                           |          |                          |                           |

|---------------|----------|---------------------------|----------|--------------------------|---------------------------|

| L             | <u>C</u> | <u>Area</u>               | <u>C</u> | <b>Area</b> mim          | Area Device               |

| 1mm           | 102 fF   | <b>388 um<sup>2</sup></b> | 102 fF   | 10 um <sup>2</sup>       | 2.7 um <sup>2</sup>       |

| 2mm           | 208 fF   | 554 um <sup>2</sup>       | 208 fF   | 14 um <sup>2</sup>       | <b>3.9 um<sup>2</sup></b> |

| 3mm           | 325 fF   | 692 um <sup>2</sup>       | 325 fF   | <b>18 um<sup>2</sup></b> | <b>4.9 um<sup>2</sup></b> |

| 4mm           | 450 fF   | 815 um <sup>2</sup>       | 450 fF   | 21 um <sup>2</sup>       | <b>5.8 um<sup>2</sup></b> |

| 5mm           | 575 fF   | 921 um <sup>2</sup>       | 575 fF   | 24 um <sup>2</sup>       | 6.5 um <sup>2</sup>       |

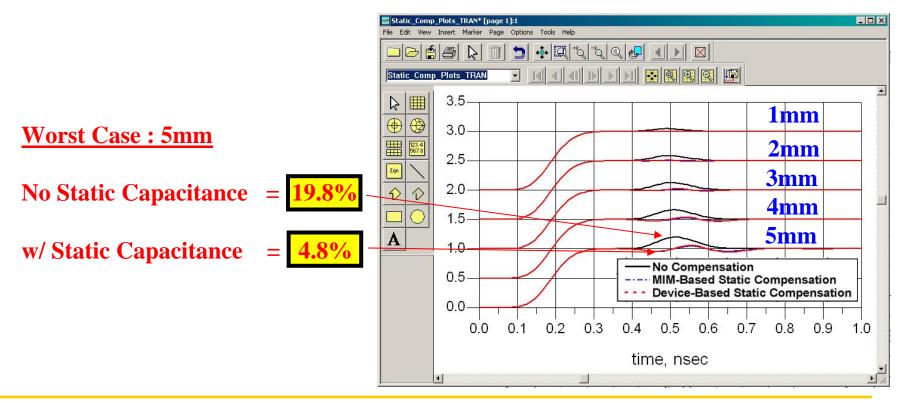

### **Experimental Results: Static Compensator**

#### • Time Domain Analysis (TDR)

- Simulation Performed using

Advanced Design System from Agilent

| $Length_{wb}$ | $\Gamma_{No-Comp}$ | $\Gamma_{MIM-Comp}$ | $\Gamma_{Device-Comp}$ |

|---------------|--------------------|---------------------|------------------------|

| 1 mm          | 4.5%               | 0.05%               | 0.5%                   |

| 2 mm          | 8.7%               | 0.4%                | 1.2%                   |

| 3 mm          | 12.7%              | 1.3%                | 2.4%                   |

| 4 mm          | 16.4%              | 2.7%                | 4.1%                   |

| 5 mm          | 19.8%              | 4.8%                | 6.0%                   |

"Impedance Matching In VLSI Packaging"

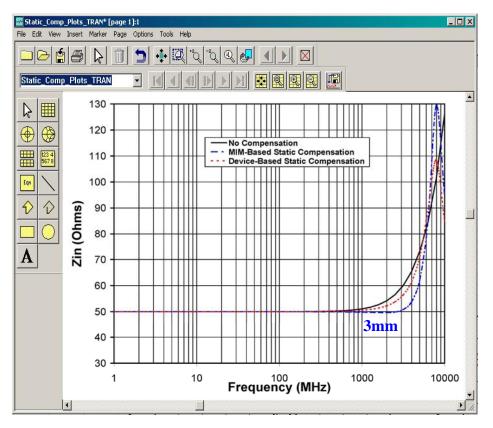

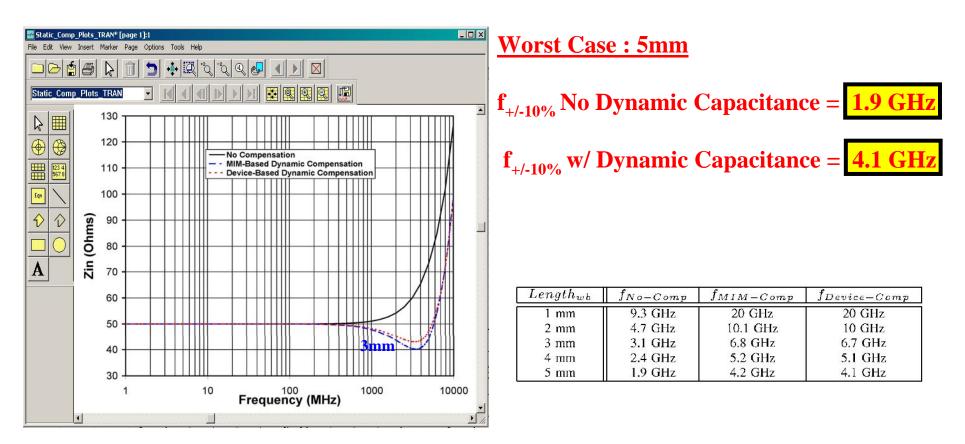

## **Experimental Results: Static Compensator**

### • Frequency Domain Analysis $(Z_{in})$

Worst Case : 5mm

$f_{+,-10\%}$  w/ Static Capacitance = 3.0 GHz

| $Length_{wb}$ | $f_{No-Comp}$ | $f_{MIM-Comp}$ | $f_{Device-Comp}$ |

|---------------|---------------|----------------|-------------------|

| l mm          | 9.3 GHz       | 14 GHz         | 12 GHz            |

| 2 mm          | 4.7 GHz       | 7.1 GHz        | 5.7 GHz           |

| 3 mm          | 3.1 GHz       | 4.8 GHz        | 3.8 GHz           |

| 4 mm          | 2.4 GHz       | 3.7 GHz        | 2.9 GHz           |

| 5 mm          | 1.9 GHz       | 3.0 GHz        | 2.5 GHz           |

### • Limitations of Approach

- Process/Design variation in wire bonds and capacitors lead to error

- Each wire bond must be evaluated for compensation requirements

#### Possible Enhancement

- Altering compensation capacitance after fabrication

- i.e., Dynamic Compensator

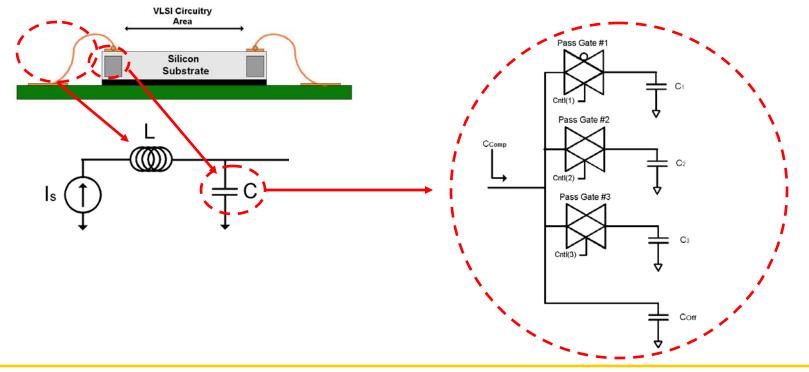

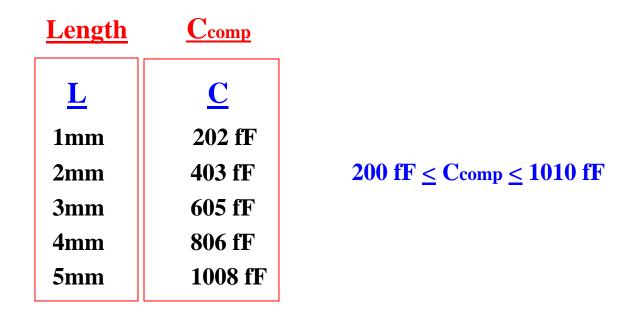

### • Programmable capacitance is placed on-chip

- On-chip capacitance is close enough to alter wire bond impedance

- Active circuitry on-chip can switch in different amounts of capacitance

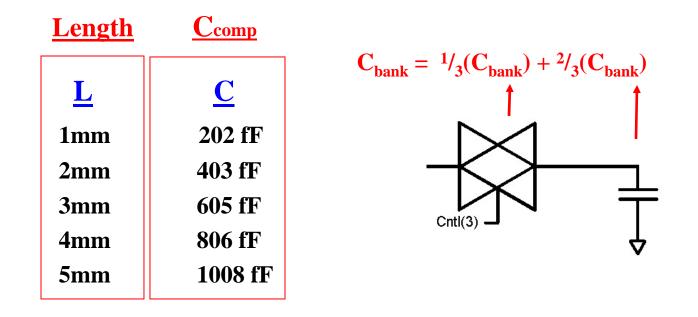

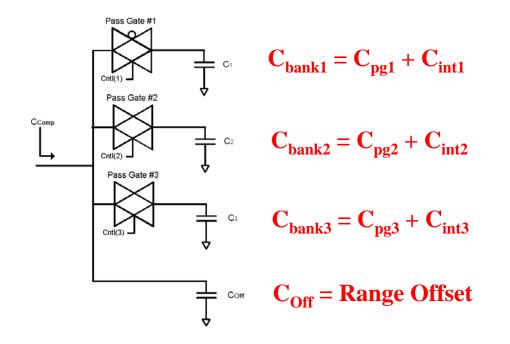

#### • Pass Gates are used to switch in on-chip capacitors

- Pass gates connect on-chip capacitance to the wire bond inductance

- Pass gates have control signals which can be programmed after fabrication

"Impedance Matching In VLSI Packaging"

• On-Chip circuitry is independent of package

- Compensation works across multiple package technologies

- This decouples IC and Package design

### • On-Chip capacitor sizing

- The on-chip capacitance performs the compensation to  $50\Omega$

- The circuit must cover the entire range of wire bond inductances

- The diffusion capacitance of the pass gates must be included in the analysis

### Compensator Design

- The on-chip capacitance performs the compensation to  $50\Omega$

- The diffusion capacitance of the pass gates must be included in the analysis

#### Capacitance Design

- Pass Gates are sized to drive the on-chip capacitance

- Each *bank* of capacitance includes the pass gates

#### Capacitance Design

- Again, both MIM and Device-based capacitors are evaluated for area

|              | MIM-Based                  | Device-Based               |  |

|--------------|----------------------------|----------------------------|--|

| Component    | Area (W $\times$ L)        | Area (W $\times$ L)        |  |

| Pass Gate #1 | $32.4 \mu m \ge 0.1 \mu m$ | $32.4 \mu m \ge 0.1 \mu m$ |  |

| Pass Gate #2 | $62.5 \mu m \ge 0.1 \mu m$ | $62.5 \mu m \ge 0.1 \mu m$ |  |

| Pass Gate #3 | 129.6µm x 0.1µm            | 129.6µm x 0.1µm            |  |

| $C_{off}$    | 8.5µm x 8.5µm              | 2.5µm x 2.5µm              |  |

| $C_1$        | $11 \mu m \ge 11 \mu m$    | 3.3µm x 3.3µm              |  |

| $C_2$        | 15.5μm x 15.5μm            | 4.6µm x 4.6µm              |  |

| $C_3$        | 22µm x 22µm                | 6.6µm x 6.6µm              |  |

| Total        | 65µm x 65µm                | 25µm x 25µm                |  |

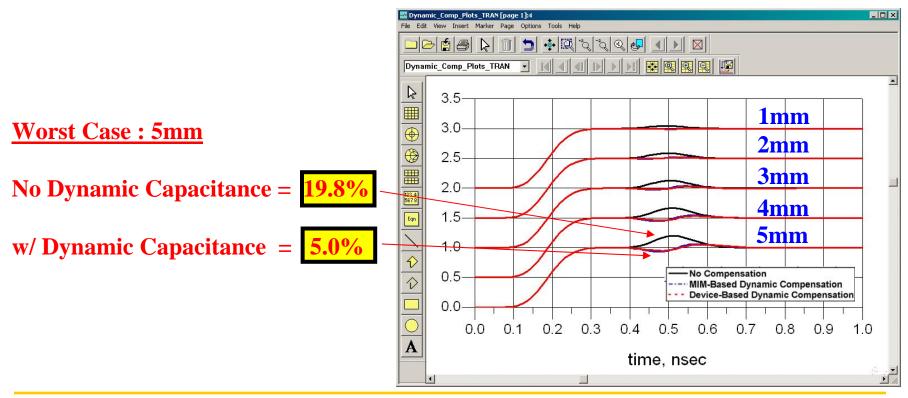

# **Experimental Results: Dynamic Compensator**

#### • Time Domain Analysis (TDR)

- Simulation Performed using Advanced Design System from Agilent

| $Length_{wb}$ | $\Gamma_{No-Comp}$ | $\Gamma_{MIM-Comp}$ | $\Gamma_{Device-Comp}$ | Setting |

|---------------|--------------------|---------------------|------------------------|---------|

| 1 mm          | 4.5%               | 1.0%                | 1.0%                   | 001     |

| 2 mm          | 8.7%               | 1.8%                | 1.3%                   | 011     |

| 3 mm          | 12.7%              | 3.6%                | 3.0%                   | 100     |

| 4 mm          | 16.4%              | 4.3%                | 3.3%                   | 110     |

| 5 mm          | 19.8%              | 6.0%                | 5.0%                   | 111     |

"Impedance Matching In VLSI Packaging"

# **Experimental Results: Dynamic Compensator**

### • Frequency Domain Analysis (Z<sub>in</sub>)

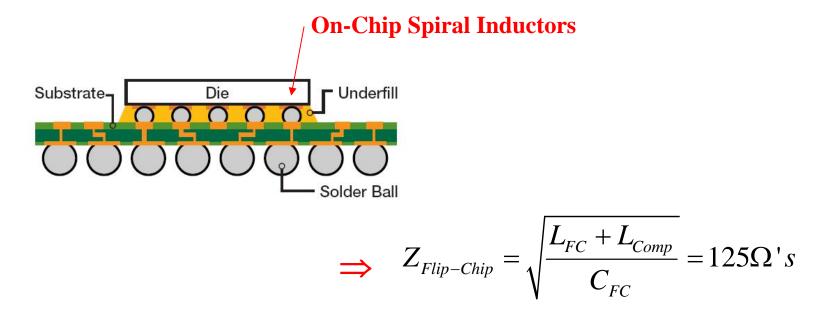

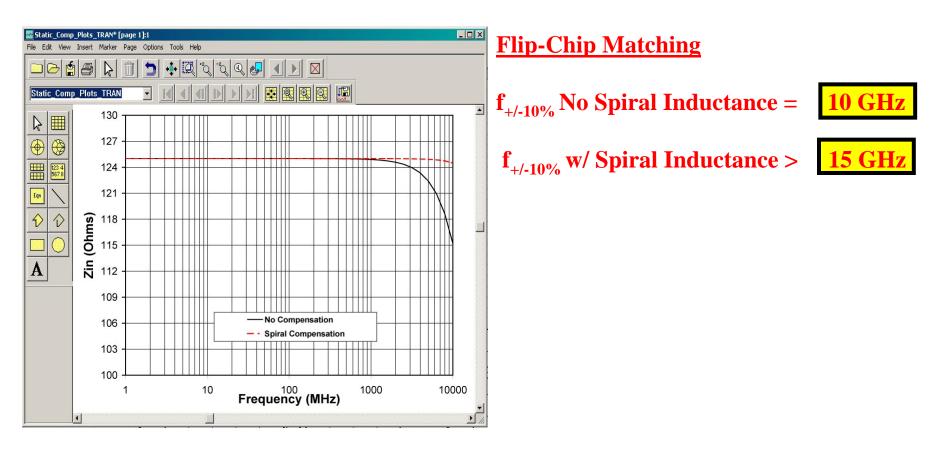

### **Inductive Compensator**

- The same theory can be applied to capacitive interconnect

- Spiral Inductors can be added on-chip

- On-chip inductance is close enough to alter capacitive interconnect impedance

- Spiral inductors are a proven on-chip technology

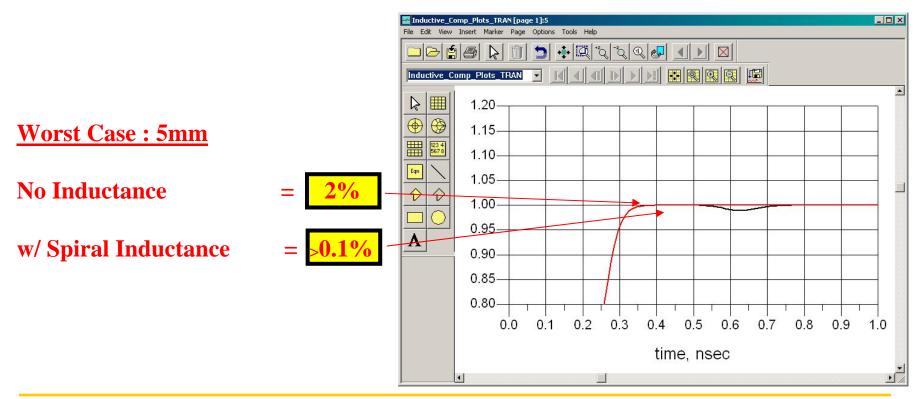

# **Experimental Results: Inductor Compensator**

### • Time Domain Analysis (TDR)

- Simulation Performed using Advanced Design System from Agilent

"Impedance Matching In VLSI Packaging"

# **Experimental Results: Inductive Compensator**

### • Frequency Domain Analysis (Z<sub>in</sub>)

### Summary

- Package Interconnect causes reflections which limits system performance

- The move toward Advanced Packaging is Resisted due to Cost

- Adding On-Chip & On-Package capacitors does not add cost

- A Static and Dynamic Compensation Approach can match the package interconnect impedance to the system

- The same approach can be applied to future interconnect structures which look capacitive

# **Thank You**